研究开发内容

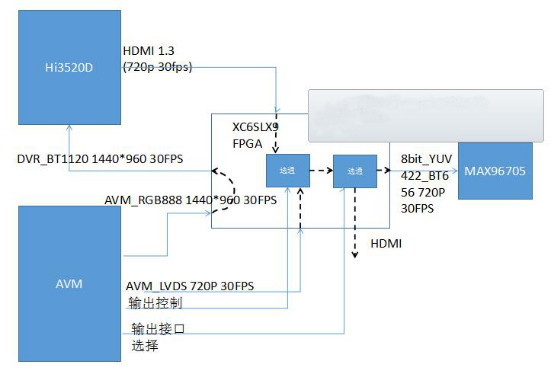

1、使用Verilog语言开发基于Xilinx XC6SLX9 FPGA平台的视频接口逻辑设计。

2、实现HDMI 1.3 720p 30fps 视频接收,并转成BT.656 720p 30fps格式数据输出或HDMI720p 30fps信号输出。

3、实现FPD 720p 30fps 视频接收,并转成BT.656 720p 30fps格式数据输出或HDMI720p 30fps信号输出。

4、实现RGB888 1440x960 30fps 视频接收,并转成BT.1120 1440x960 30fps格式数据输出。

5、实现AVM对HDMI输入、FPD信号输入的二选一输出,二选一的输出可切换成HDMI或BT.656 720p 30fps输出。

本项目使用HDMI协议转换,若使用FPGA实现,非IPcore的情况下,需要消耗较多的逻辑资源,目前的s6不能满足需求,升级FPGA规格会增加较高的成本,因此考虑FPGA+HDMI 接收IC的方案实现。

|

型号 |

成本(参考) |

性能评估 |

|

ADV7610 |

30.00 |

传输差分信号(TMDS)时钟频率:165 MHz |

|

DS16EV5110ASQ |

25.00 |

传输差分信号(TMDS)时钟频率:250 MHz |